#### **General Description**

The MAX5911/MAX5912 are fully integrated hot-swap switches for negative supply rails. These devices allow the safe insertion and removal of circuit cards into live backplanes or ports without causing problematic glitches on the negative power-supply rail. They also monitor various circuit parameters and disconnect the load if a fault condition occurs, alerting the host with a logic-level FAULT output. The MAX5911/MAX5912 operate over a voltage range of -16V to -65V and are designed to permit hot plugging of an IP phone into a hub, but are not limited to that operation.

During startup, an internal power FET regulates the current between the backplane power source and the load to 280mA for MAX5911 and 415mA for MAX5912. After startup, the FET is fully enhanced to reduce its on-resistance. To ensure robust operation, the MAX5911/ MAX5912 contain built-in safety features that prevent damage to the internal FET. They include an enable input, which responds to positive logic signals (+3.3V or +5V), allowing the host system to disconnect the load. ENABLE is also used to reset the device after a latching fault condition occurs.

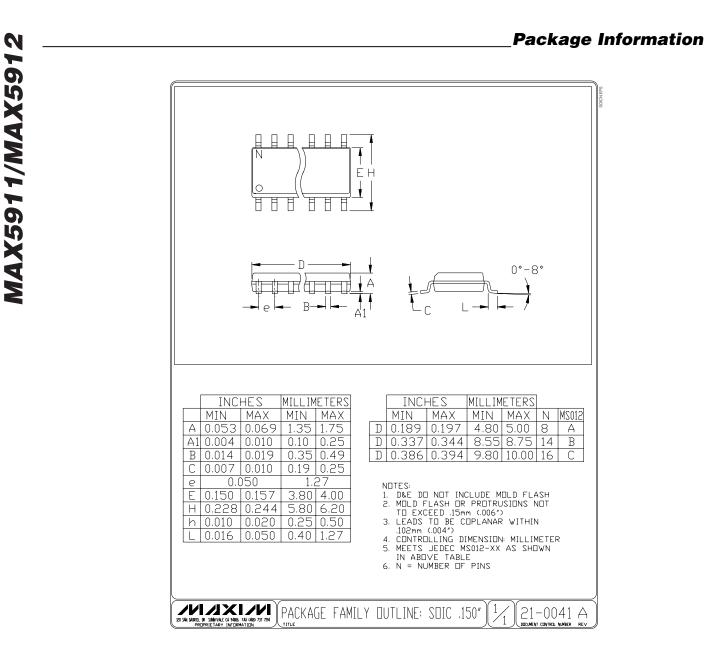

The MAX5911/MAX5912 Simple Swapper<sup>™</sup> hot-swap ICs monitor four parameters for these fault conditions: undervoltage lockout (UVLO), power-not-good, zerocurrent detection, and thermal shutdown. These devices are available in the extended temperature range, -40°C to +85°C. The MAX5911 and MAX5912 come in 8-pin and 16-pin SOIC packages, respectively.

P Phones Network Routers Network Switches Internet Appliances Power-Over-LAN

**Applications**

#### Typical Operating Circuit V<sub>IN</sub> (-48V) Vou *ก*и ЛХГЛИ +3.3\ 0.1u Т MAX5911 MAX5912 JVI 0 I OAD $\gtrsim$ 3.3k $\Omega$ ALII T POSITIVE FNARI F LOGIC DGND AGND

####

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### Features

- Provides Safe Hot Swap for -16V to -65V Power Supplies

- 280mA Current Limit for MAX5911

- 415mA Current Limit for MAX5912

- Zero-Current Load Disconnect

- Integrated Power FET

- Status Output Reports Fault Condition

- Internal Switch-Protection Circuitry

- Built-In Thermal Shutdown

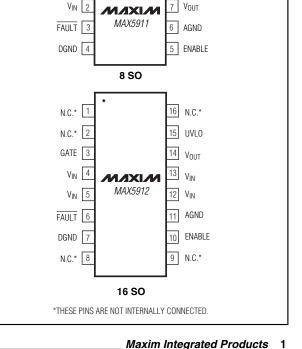

TOP VIEW

GATE 1

DGND Can Vary Up to ±5V with Respect to AGND

#### \_Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX5911ESA | -40°C to +85°C | 8 SO        |

| MAX5912ESE | -40°C to +85°C | 16 SO       |

Simple Swapper is a trademark of Maxim Integrated Products, Inc.

#### Pin Configurations

8 UVLO

#### **ABSOLUTE MAXIMUM RATINGS**

Voltages are with respect to AGND, unless otherwise noted.

| V <sub>IN</sub>         | +0.3V to -70V                     |

|-------------------------|-----------------------------------|

| Vout                    | +0.3V to (V <sub>IN</sub> - 0.3V) |

| ENABLE to DGND          | 0.3V to +11V                      |

| ENABLE to VIN           | 0.3V to +70V                      |

| FAULT to DGND           | 0.3V to +11V                      |

| UVLO to V <sub>IN</sub> | 0.3V to +11V                      |

| DGND                    | 5V to +5V                         |

| DGND to VIN             | 0.3V to +70V                      |

| FAULT Sink Current      |                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL SPECIFICATIONS**

(V<sub>IN</sub> = -48V, AGND = DGND = 0, UVLO = open circuit, V<sub>ENABLE</sub> = +3.3V, and T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                      | SYMBOL                | CONDITIONS                                                              |         | MIN  | ТҮР  | MAX  | UNITS |

|------------------------------------------------|-----------------------|-------------------------------------------------------------------------|---------|------|------|------|-------|

| Input Voltage Range                            | VIN                   |                                                                         |         | -65  |      | -16  | V     |

| Supply Current                                 | l <sub>IN</sub>       | Measured at AGND at the end of output voltage slew                      |         |      | 1.5  | 2.5  | mA    |

| Maximum V <sub>OUT</sub> Current               | I <sub>OUT(MAX)</sub> | $V_{OUT} = V_{IN} + 5V$                                                 | MAX5911 | -310 | -280 | -250 | mA    |

|                                                |                       |                                                                         | MAX5912 | -457 | -415 | -373 |       |

| DMOS On-Resistance                             | R <sub>DS(ON)</sub>   | MAX5911 I <sub>OUT</sub> = -225mA,<br>MAX5912 I <sub>OUT</sub> = -350mA |         |      | 2.5  | 4    | Ω     |

| V <sub>OUT</sub> Leakage Current               |                       | Measured on V <sub>OUT</sub> when internal DMOS is shut off             |         |      |      | 10   | μA    |

| ENABLE Low Voltage                             | VIL                   | Referenced to DGND                                                      |         |      |      | 0.8  | V     |

| ENABLE High Voltage                            | VIH                   | Referenced to DGND                                                      |         | 2.0  |      |      | V     |

| ENABLE High Input Current                      | IIН                   | $V_{\text{ENABLE}} = +3.3V$                                             |         |      | 140  | 300  | μΑ    |

| ENABLE Low Pulse Width<br>(Note 1)             | tepw                  |                                                                         |         | 200  |      |      | ns    |

| FAULT Output Low Voltage                       | VOL                   | IFAULT = 3mA                                                            |         |      |      | 0.4  | V     |

| FAULT Output Leakage Current                   | ЮН                    | $V_{FAULT} = +3.3V$                                                     |         |      |      | 10   | μΑ    |

| Zero-Current Detection<br>Threshold            | IFTH                  | Decreasing load current                                                 |         | -12  | -8   | -4   | mA    |

| Zero-Current Detection<br>Threshold Hysteresis | IF <sub>HY</sub>      |                                                                         |         |      | 1.5  |      | mA    |

| Zero-Current Detection Delay<br>(Note 2)       | IFDEL                 |                                                                         |         | 280  | 350  | 520  | ms    |

| Current-Limit Delay (Note 3)                   | <b>t</b> LIMIT        | V <sub>OUT</sub> shorted to AGND                                        |         |      | 10   | 20   | μs    |

| Power-Good Threshold                           | VPG                   | IVIN - VOUTI, IVIN - VOUTI decreasing                                   |         | 1.95 | 2.15 | 2.35 | V     |

| Power-Good Hysteresis                          | PG <sub>HYS</sub>     | % of V <sub>PG</sub>                                                    |         |      | 5    |      | %     |

#### **ELECTRICAL SPECIFICATIONS (continued)**

$(V_{IN} = -48V, AGND = DGND = 0, UVLO = open circuit, V_{ENABLE} = +3.3V, and T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at T\_A = +25°C.)

| PARAMETER                                | SYMBOL | CONDITIONS                                                                                |     | ТҮР    | MAX | UNITS |

|------------------------------------------|--------|-------------------------------------------------------------------------------------------|-----|--------|-----|-------|

| Power-Not-Good Output Delay<br>(Note 4)  | PGDEL  | After IV <sub>IN</sub> - V <sub>OUT</sub> I increases above<br>(VPG + PG <sub>HYS</sub> ) | 8   | 14     | 20  | ms    |

| Thermal Shutdown Temperature<br>(Note 5) | TJ     |                                                                                           |     | 140    |     | °C    |

| Default UVLO                             |        | UVLO open circuit, IVINI increasing                                                       | -30 | -28    | -26 | V     |

| UVLO Hysteresis                          |        | UVLO open circuit, percentage of UVLO threshold                                           |     | 12     |     | %     |

| UVLO Comparator Threshold                |        | Referenced to V <sub>IN</sub> , UVLO open circuit,<br>IV <sub>IN</sub> I increasing       |     | +1.258 |     | V     |

| UVLO Input Resistance                    | Ruvlo  |                                                                                           |     | 95     |     | kΩ    |

Note 1: Minimum ENABLE low pulse width required to unlatch fault condition.

Note 2: The delay from IOUT falling below the zero-current threshold until FAULT is latched low and VOUT is disabled.

Note 3: The time from an output overcurrent or short-circuit condition until the output goes into current limit.

Note 4: The time from V<sub>OUT</sub> falling until FAULT is asserted low. FAULT is not latched for Power-Not-Good condition.

Note 5: When the device goes into thermal shutdown, the output is disabled and FAULT is latched low.

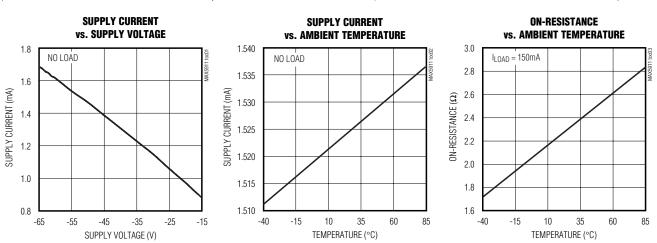

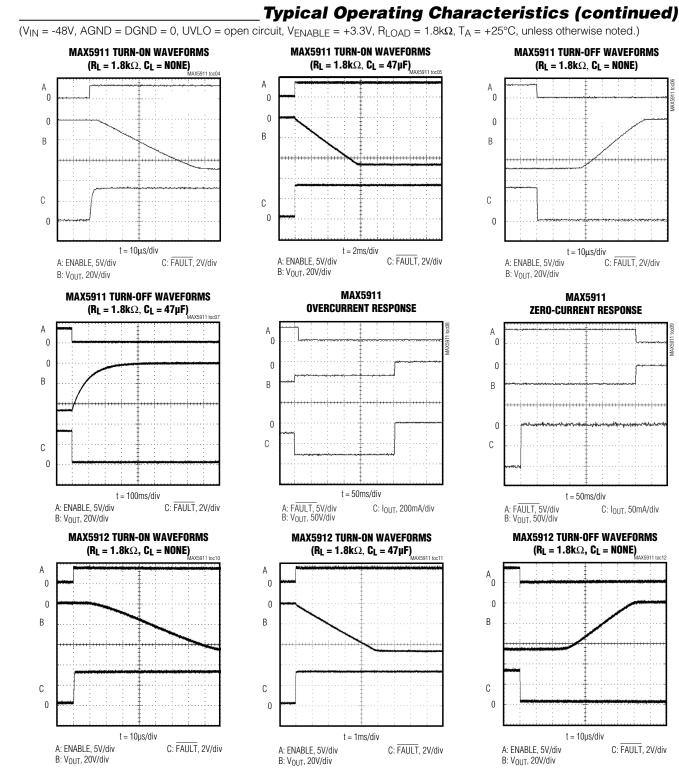

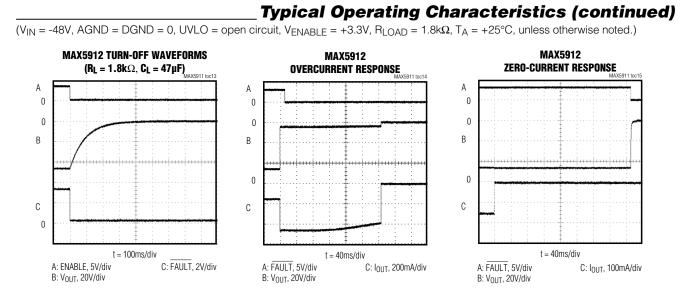

#### **Typical Operating Characteristics**

$(V_{IN} = -48V, AGND = DGND = 0, UVLO = open circuit, V_{ENABLE} = +3.3V, R_{LOAD} = 1.8k\Omega, T_A = +25^{\circ}C$ , unless otherwise noted.)

#### Pin Description

| PIN     |                | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                |  |  |  |

|---------|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX5911 | MAX5912        |                 |                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1       | 3              | GATE            | Gate of the Internal Power MOSFET. Normally leave open circuit. To slow down the output voltage ramp, connect two capacitors, one to $V_{\rm IN}$ and one $V_{\rm OUT}.$ See GATE Connections for details.                                                                                                              |  |  |  |

| 2       | 4, 5, 12, 13   | V <sub>IN</sub> | Voltage Input Terminal. Bypass $V_{IN}$ , to AGND with a 0.1µF capacitor to improve noise immunity.                                                                                                                                                                                                                     |  |  |  |

| 3       | 6              | FAULT           | Fault Logic Output, open-drain. Tie $\overline{FAULT}$ to the positive logic supply with a 3.3k $\!\Omega$ resistor. Referenced to DGND.                                                                                                                                                                                |  |  |  |

| 4       | 7              | DGND            | Digital Ground. Ground reference level for the external positive logic, $\overline{FAULT}$ , and ENABLE. DGND can vary up to $\pm 5V$ with respect to AGND to accommodate differential ground voltages in large systems.                                                                                                |  |  |  |

| 5       | 10             | ENABLE          | ENABLE Input. Turns on and off the internal FET. ENABLE is a positive logi<br>level input referenced to DGND. Drive ENABLE high to enable V <sub>OUT</sub> . Drive<br>ENABLE low to disable V <sub>OUT</sub> . Pulse ENABLE low to reset the MAX5911/<br>MAX5912 after a latched fault condition occurs.                |  |  |  |

| 6       | 11             | AGND            | Analog Ground. Ground reference level for VIN, VOUT, and UVLO.                                                                                                                                                                                                                                                          |  |  |  |

| 7       | 14             | Vout            | Voltage Output Terminal                                                                                                                                                                                                                                                                                                 |  |  |  |

| 8       | 15             | UVLO            | Undervoltage Lockout Input. Leave UVLO open circuit for default setting of -28V. Alternatively, UVLO can be connected to a resistive divider to set the lockout voltage (see the <i>Changing the Undervoltage Lockout Setting</i> section). The comparator threshold level is +1.258V with respect to V <sub>IN</sub> . |  |  |  |

| _       | 1, 2, 8, 9, 16 | N.C.            | No Connection. No internal connection.                                                                                                                                                                                                                                                                                  |  |  |  |

# MAX5911/MAX5912

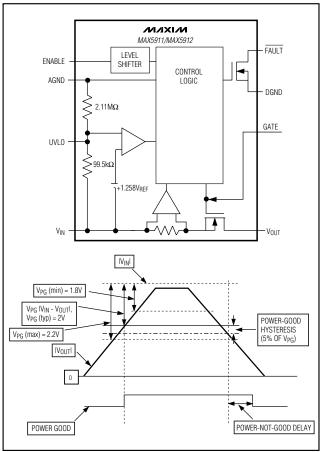

Figure 1. Functional Block Diagram

#### **Detailed Description**

Figure 1 shows a functional block diagram. The MAX5911/MAX5912 are hot-swap switches for negative supply rails. The devices allow the safe insertion and removal of circuit cards into live backplanes or ports without causing undue glitches on the negative power-supply rail. They operate over the -16V to -65V voltage range. The devices act as a current regulator, using their on-board FET to limit the amount of current drawn from the backplane to 280mA for MAX5911 and 415mA for MAX5912. If the load current exceeds that current limit, the internal switch behaves like a constant current source.

The MAX5911/MAX5912 monitor the input voltage, the output voltage, the output current, and the die temperature. They assert their FAULT output if they detect an error condition.

A zero-current load disconnect feature activates if the load current drops below 8mA for over 350ms. They also

include an enable input that responds to positive logic, allowing the host system to turn the FET switch on or off. The enable input is also used to reset the devices after an error condition has latched the output FET off.

#### Normal Operation

#### Startup

When power is first applied with ENABLE high, or when ENABLE is asserted, the MAX5911/MAX5912 limit the current to the load to 280mA/415mA. If the output voltage has not reached the power-good threshold within the 14ms power-good delay, FAULT is pulled low. FAULT stays low until the output voltage exceeds the power-good threshold, at which time it is released and becomes high impedance.

#### **Undervoltage Lockout Fault**

If  $|V_{IN}| \leq |UVLO|$ , where UVLO is the desired voltage at which the UVLO fault occurs, FAULT is pulled low and the internal FET is turned off. If the condition persists for over 350ms (IF<sub>DEL</sub>), the FET is latched off. The default UVLO voltage is -28V, but it can be adjusted using an external resistive divider (see the *Changing the Undervoltage Lockout Setting* section). Once the FET is latched off, ENABLE must be pulsed low then brought back high to release FAULT and enable V<sub>OUT</sub>.

#### **Thermal Shutdown Fault**

The MAX5911/MAX5912 monitor their internal die temperatures. If the temperature of the die exceeds +140°C, FAULT is pulled low and the internal FET is latched off. ENABLE must be pulsed low and then brought high again to reset the FET latch, and release FAULT, provided the die is below the thermal shutdown temperature by 5°C (typ).

#### **Power-Not-Good Fault**

If IV<sub>IN</sub> - V<sub>OUT</sub>I is more than the power-good threshold for over 14ms, FAULT is pulled low. When the output voltage exceeds the power-good threshold, FAULT is released. FAULT output is not latched during a power-not-good fault.

#### **Zero-Current Detection**

If the load current drops below 8mA for over 350ms, FAULT is pulled low and the FET is latched off. ENABLE must be pulsed low and then brought high again to release FAULT and enable V<sub>OUT</sub>.

#### **Applications Information**

#### **Chosing A Device**

The MAX5911 will output up to 280mA (typ) and the MAX5912 up to 415mA (typ). In applications where high heat is expected, use the MAX5912 for its superior

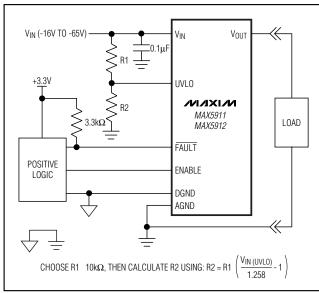

Figure 2. UVLO Voltage Set by an External Resistive Divider

heat dissipation properties, and always solder all of its  $V_{IN}$  pins to a large section of circuit board copper.

#### **Logic Control**

The enable input responds to +3.3V logic signals and will force the internal FET off if it is pulled low. This feature allows the host to disconnect the load from the power bus if required. Additionally, all fault conditions that latch the internal FET off must be cleared by pulsing ENABLE low for at least 200ns, then reasserting ENABLE before normal operation can resume.

#### **GATE Connections**

GATE connects to the gate of the internal N-channel power MOSFET. Normally this pin should be left open circuit. To slow down the voltage ramp at V<sub>OUT</sub>, connect capacitors from GATE to V<sub>OUT</sub> and V<sub>IN</sub>. Size the capacitors so that the GATE to V<sub>IN</sub> capacitor is ten times the size of the GATE to V<sub>OUT</sub> capacitor. This technique to slow down the output voltage ramp will also cause the output discharge time to increase if the capacitor values exceed about 1nF. Additionally, this technique will cause the time delay for a power-not-good fault to increase.

#### FAULT Output

The FAULT output is open-drain and is pulled low if the MAX5911/MAX5912 detect an undervoltage fault, a thermal fault, a power-not-good fault, or a zero-current fault. See the *Normal Operation* section for specific details of fault operation. Connect FAULT to the logic supply with a pullup resistor;  $3.3k\Omega$  is sufficient in most cases.

#### Changing the Undervoltage Lockout Setting

The UVLO value defaults to -28V if the UVLO pin is left open circuit. The lockout voltage can be changed with a resistive divider. Connect the divider from V<sub>IN</sub> to AGND, and connect the center node of the divider to the UVLO pin. Figure 2 shows an example circuit. Use  $R1 \leq 10k\Omega$ , then calculate R2 using:

$$R2 = R1 \times \left(\frac{V_{IN(UVLO)}}{1.258} - 1\right)$$

where  $V_{IN(UVLO)}$  is the desired lockout voltage.

Chip Information

TRANSISTOR COUNT: 1021 PROCESS: BICMOS

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2001 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.